TECHNOLOGY NEWS

Frequency Synthesis and Number Theory: The Diophantine Approach

Frequency synthesis is essential to modern electronic systems such as wireless and wired communication, digital computers, radars, timing and navigation (GPS), scientific instruments, medical systems and many others.

In principle, a frequency synthesizer is a frequency multiplier; it multiplies an input reference frequency fin by a positive factor a = fout / fin which may be fixed or variable depending on the application and may very well be less than one. In practice, factor a is a rational number, i.e. a = N / R, meaning that (groups of) N cycles of the synthesized output signal correspond to (groups of) R cycles of the input reference one. A frequency synthesizer has a mechanical analog to a gear pair where the angular frequency of the “output” gear is N / R times that of the “input” gear, when the two gears have R and N teeth respectively.

Addition and subtraction of frequencies are done by signal mixing and are also used in frequency synthesis [1]. The mechanical equivalent of the mixer is the differential, which adds or subtracts angular frequency. Multiplication by rational factors, addition and subtraction of frequencies can be used in combination to generate more values for the input-output multiplication factor, a, in the form of algebraic expressions involving only these three operations and rational numbers.

The approximation of real numbers using such algebraic expressions, involving only rational numbers which are preferably derived from the fractions of small positive integers, has attracted the attention of engineers and mathematicians since antiquity. One reason is that such expressions model the operation of compound gear boxes of mechanical calculators. The Antikythera Mechanism [2] and the Huygens planetarium [3] are two famous examples of such mechanical systems. In the modern era, the approximation problem was transferred to electronic frequency synthesis domain [4]. Complex frequency synthesizers with multiple loops (nested or not) were popular in the past few decades and they are still used, especially when very spectrally clean signals are needed, despite their significant size, weight and cost. Frequency synthesis architectures used in atomic clocks are also associated with number approximation techniques [4].

Integer-N Phase Locked Loops (PLL)s are the most popular basic frequency synthesizers. They perform frequency multiplication by a = N / R, where N is their feedback divider and R is their pre-scaler divider [1]. Small values are preferable for both dividers, especially for pre-scaler R because fin / R , which is the phase-comparator frequency of the PLL, is desirable to be as high as possible for agility and noise performance. Frequency fin / R is also the smallest frequency step (resolution) of the PLL, assuming R is fixed, which is typical.

Another class of frequency synthesizers is that of Fractional-N PLLs. They provide good frequency resolution and agility with low complexity hardware, but typically with worse spectral purity than that of the Integer-N, multi-loop ones. Their operation is based on frequency interpolation [1].

A relatively newer frequency synthesis approach is the Direct Digital Synthesis (DDS), or Numerical Oscillators [4]. Here, the values of the sine or cosine functions, corresponding to phase values that form an arithmetic sequence, are digitally generated, put in time order based on an external clock, converted to analog voltages or currents, and, low-pass filtered to provide a sinusoidal signal at the output. DDS has advantages in terms of frequency resolution and agility but lacks spectral purity compared to the multi-loop approach due to truncation errors in the phase and amplitude conversion [4].

A new frequency synthesis methodology, named Diophantine Frequency Synthesis (DFS) was introduced in [5]. It is based on mathematical properties of integer numbers and Diophantine equations [6] and achieves very high resolution (e.g. 10–10 fractional resolution), agility and signal purity with relatively low complexity. The DFS synthesizer has a modular structure with conventional circuitry.

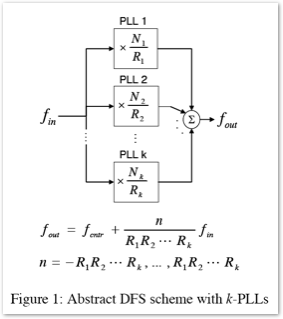

A new frequency synthesis methodology, named Diophantine Frequency Synthesis (DFS) was introduced in [5]. It is based on mathematical properties of integer numbers and Diophantine equations [6] and achieves very high resolution (e.g. 10–10 fractional resolution), agility and signal purity with relatively low complexity. The DFS synthesizer has a modular structure with conventional circuitry. Conceptually, DFS architectures can be thought of as composed out of two or more Integer-N PLLs which are driven by the same reference signal and whose output frequencies are added (or subtracted) to give the output frequency of the synthesizer. This is shown in Fig. 1 where R1, R2, ..., Rk and N1, N2, ..., Nk are the pre-scaler and feedback dividers of the PLLs respectively.

The advantages of DFS result from the mathematical way the values of the pre-scaler dividers are chosen and the feedback dividers are programmed. If R1, R2, ..., Rk are pair-wise relatively prime, DFS guaranties a frequency step equal to fin / (R1R2...Rk) while the frequency steps (and phase-comparator frequencies) of the individual PLLs are fin / Ri, i = 1, 2, ..., k. Note that R1, R2, ..., Rk can be small numbers while the product R1R2...Rk can be a very large one. Moreover the number of output frequency steps is 2R1R2...Rk + 1. The key to practical use of DFS is a decomposition algorithm to arrive at the coefficients N1, N2, ..., Nk. An efficient such algorithm with tight bounds on the range of the integer coefficients Ri is given in [5].

DFS can be used in frequency ranges much higher than those achieved by current DDS technology; it results in more compact systems than standard multi-loop architectures and offers better agility and signal purity than Fractional-N synthesizers.

These properties make DFS a convenient choice for applications requiring high resolution, agility and wide output frequency range, especially in the multi-GHz range. UWB and software radio, radars and instrumentation systems are just a few examples. DFS synthesizers have been demonstrated in [7] and [8].

More information on DFS as well as the latest developments related to it can be found at www.ece.jhu.edu/~pps.

References:

[1] W. F. Egan, Frequency Synthesis by Phase Lock, Second Edition, New York: Wiley, 1999.

[2] T. Freeth et. al., “Decoding the ancient Greek astronomical calculator known as the Antikythera mechanism”, Nature, vol. 444, pp. 587–591, Nov. 2006.

[3] H. Hoijmaijers, Telling Time - Devices for Time Measurement in Museum Boerhaave, Boerhaave National Museum of the History of Science, Leiden (The Netherlands), 2005.

[4] V. F. Kroupa (Ed.), Direct Digital Frequency Synthesizers, New York: Wiley-IEEE Press, Nov. 1998.

[5] P. P. Sotiriadis, “Diophantine frequency synthesis,” IEEE Trans. on Ultrasonics, Ferroelectrics, and Frequency Control, vol. 53, no. 11, pp. 1988–1998, Nov. 2006.

[6] D. E. Flath, Introduction to Number Theory, New York: Wiley, 1989.

[7] P. P. Sotiriadis, “Diophantine frequency synthesis: a forward two - PLL architecture case-study,” IEEJ Analog VLSI Workshop 2007.

[8] P. P. Sotiriadis and G. L. Weaver, ``A diophantine frequency synthesizer for the examination of high spectral purity,” IEEE International Frequency Control Symposium 2007.

Paul P. Sotiriadis, Department of Electrical and Computer Engineering, John Hopkins University (Email: pps at ieee dot org)

This article was recommended by Andreas Demosthenous.